AMD Vitis™ HLS

Empowers RTL Designers with Faster Verification and Design Iteration

AMD Vitis™ HLS for Intuitive Design and Productivity

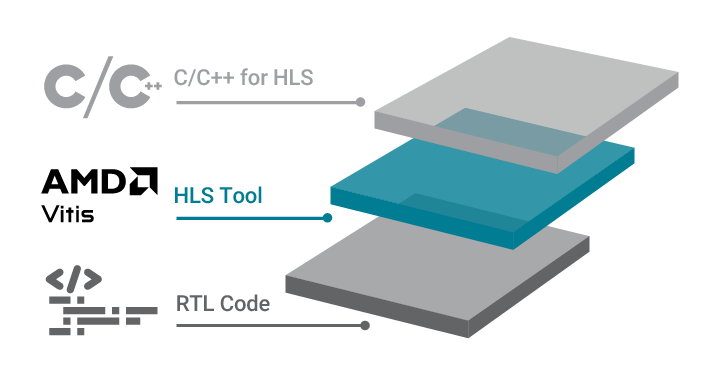

The AMD Vitis™ HLS tool allows users to easily create complex FPGA algorithms by synthesizing a C/C++ function into RTL. The Vitis HLS tool is tightly integrated with both the Vivado™ Design Suite for synthesis and place & route and the Vitis™ unified software platform for heterogenous system designs and applications.

- Using the Vitis HLS flow, users can apply directives to the C code to create the RTL specific to a desired implementation.

- Multiple design architectures can be created from the C source code and a path for high-quality, correct-by-construction RTL is enabled.

- C simulation can be used to validate the design and allows faster iterations than a traditional RTL-based simulation.

- The Vitis HLS tool features a rich set of analysis and debugging tools that facilitate design optimization.

Design Methodology

Vitis HLS Programming Model

Vitis HLS C code is geared towards taking advantage of the benefits and characteristics offered by the architecture of AMD FPGAs.

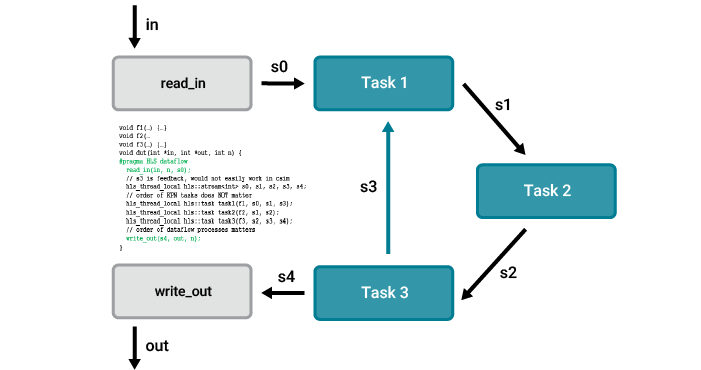

The Vitis HLS tool supports parallel programming constructs in order to model a desired implementation. These constructs include:

- HLS tasks that allow process-level concurrency

- HLS vectors that allow data-level parallelism

- HLS streams that allow communication between concurrent tasks

- Synthesis pragmas can be used to control the results. These pragmas include pipeline, unroll, array partitioning, and interface protocols.

- For additional details, see the " HLS Programmers Guide ” section in the Vitis High-Level Synthesis User Guide.

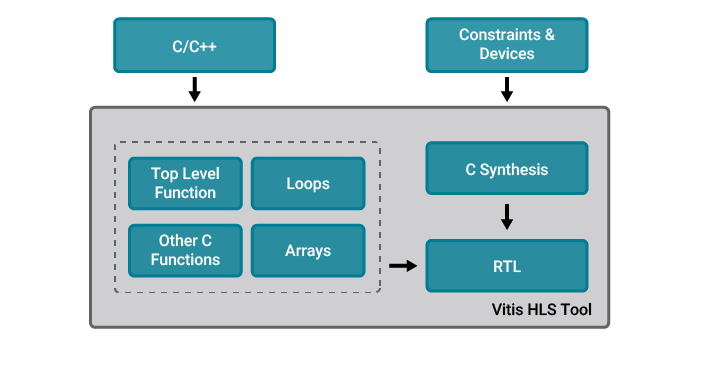

C-to-RTL Conversion

The Vitis HLS tool synthesizes different parts of C code differently:

- Top-level function arguments of the C/C++ code are synthesized into RTL I/O ports and are automatically implemented with an interface synthesis hardware protocol.

- Other C functions are synthesized to RTL blocks—maintaining the design hierarchy.

- C function loops are kept rolled or pipelined to improve performance.

- Arrays in the C code can be targeted to any memory resource, such as BRAM, LUTRAM, and URAM.

- Performance metrics, such as latency, initiation interval, loop iteration latency, and resource utilization, can be reviewed with synthesis reports.

- Vitis HLS tool pragmas and optimization directives allow for configuring the synthesis results for the C/C++ code.

Simulation and Verification

The Vitis HLS tool has built-in simulation flows to enable faster verification times:

- C simulation validates the functionality of the C code. This step is fast and uses a C test bench.

- C/RTL co-simulation reuses the C test bench to perform validation on the generated RTL—verifying that the RTL is functionally identical to the C source code.

- The flow has integrated analysis, debug, and waveform viewing capabilities as well as popular simulator support.

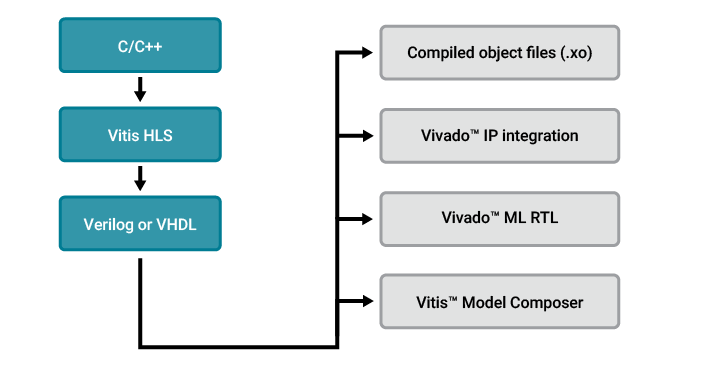

The output of the Vitis HLS tool is an RTL implementation that can be either packaged into a compiled object file (.xo) or exported to an RTL IP:

- Compiled object files (.xo) is used to create hardware acceleration functions for use in the Vitis application development flow.

- Added using the Vivado™ IP integrator tool

- Imported as an RTL block in the Vivado IDE

- Used as a single blockset in Vitis Model Composer for DSP applications

2024.1 Release Highlights

- A new stencil pragma simplifies HLS C++ code for image and video filters

New library function wizards tap into the AMD Vitis libraries github repo

- Create “Solver” and “Vision” (OpenCV compatible) IPs for AMD Vivado design tool

- Run the available library examples

Pragma for memory interface (ap_memory) can now bundle ports for AMD Vivado IP Integrator

New HLS component comparison displays side-by-side metrics for 2 or more components

Support for user-provider RTL code to replace a C++ function (black-box flow)

Code Analyzer can now disaggregate C++ struct members to fine-tune performance analysis

New user control for HLS global FSM encoding and selection of safe state

Access to Clang sanitizers during C-Simulation to perform address and initialization checks

2023.2 Release Highlights

- New Vitis™ Unified IDE for HLS components

- New Vitis HLS license requirements

- New code analyzer feature for obtaining performance estimations before running C synthesis

- Enhancements to HLS AXI Stream side-channel support

- Support for user-configurable AXI master caching

- New code complexity report to enable identifying design size issues during C synthesis

- Compile time improvements: Average compile time improvement of 20% in 2023.2 compared to 2023.1 1

2023.1 Release Highlights

- Performance improvements 2 : Average latency improvements of 5.2% in 2023.1 compared to 2022.2

- Easy way to download, view, and instantiate L1 libraries functions in the Vitis HLS tool. Watch video

- Enhanced support for AXI transactions and burst reporting within the Vitis HLS tool

2022.2 Release Highlights

- User can explicitly define task-level parallelism using the new hls::task function

- Easier to model for purely streaming designs (e.g., packet switching)

- Tool automatically infers unroll, pipeline, array partitions, and inline pragmas for better performance

- New feature to synthesize print statements from C source in the generated RTL code

- When RTL is simulated, this allows tracing the execution of a code block and the value of a variable

- hls::stream interface is now supported for FFT and FIR IPs

2022.1 Release Highlights

- Shows the runtime profile of all surviving functions in your design - i.e., those that get converted into modules

- Especially useful to see the behavior of dataflow regions after Co-simulation. Native to Vitis™ HLS - No need to launch the xsim waveform viewer anymore

- HLS what your throughput target is using #pragma hls performance

- HLS will attempt to meet target, if possible, using fewest resources

- HLS will indicate transformations performed, and if it can’t meet target will indicate limiting factor

- hls::stream enhancement where each element is an array

- Can be used to break up large array processing into smaller, pipelined pieces

2021.2 Release Highlights

- User can adopt newly introduced manual burst optimization

- A new class 'hls::burst_maxi’ is added to support manual controlling burst behavior New HLS APIs are provided to use together with the new class.

- Users need to understand AXI AMBA protocol and the hardware transaction level modeling in HLS design

- Improve HLS timing estimation accuracy. When HLS reports timing closure, Vivado™ RTL synthesis should also expect to meet timing

- Add interface adaptors report in the C-synthesis report

- Users need to know the resource impact that interface adaptors have on their design

- Interface adaptors have variable properties that impact design QoR

- Add new section in synthesis report to show list of pragmas and warnings on pragmas

- New mouse drag based zoom in and out capability

- New Overview feature that shows the full graph and allows the user to zoom in on parts of the overall graph

- All functions and loops are shown along with their simulation data

- A new Timeline Trace Viewer is now available after simulation. This viewer shows the runtime profile of your design and allows the user to remain in the Vitis HLS GUI

2021.1 Release Highlights

- New “Flow Navigator” in GUI for quick access to flow phases and reports. The contextual "synthesis, analysis, debug" views are merged into a general default context

- New synthesis report section for the BIND_OP and BIND_STORAGE directives

- A new post synthesis text report reflects the information provided in the GUI synthesis report

- The IP export and Vivado™ implementation run widgets have been redesigned with options to pass settings and constraint files to Vivado

- New function call graph viewer to visualize functions and loops which can be highlighted with an optional heatmap to detect II, latency or DSP/BRAM utilization hot spots

- Versal™ timing calibration and new controls for DSP block native floating-point operations (the -precision option for config_op)

- Alternate flushable pipeline option has been improved (free-running pipeline aka "frp")

- In Vitis, reshaping m_axi interfaces should be done via the hls::vector types

- New customization options for s_axilite and m_axi data storage which can be "auto, "uram", "bram" or "lutram" allowing you to tweak RAM utilization in your design

- In Vitis, introducing a new continuously (aka "never-ending") running mode for kernel

- The axi_lite secondary clock option has been re-instated

Success Stories

Achieve Ultra-Low Latency in an Audio DSP-to-FPGA with Vitis HLS

The Emeraude Research Team from INSA Lyon, is working on developing new signal processing techniques for embedded audio systems. The team has implemented an ultra-low latency audio DSP program using the AMD Vitis HLS tool. Click here to learn more about how the Vitis HLS tool helped the team to achieve ultra-low latency in an audio DSP-to-FPGA compilation. Customer Case Study

Faster Design Space Exploration with Vitis HLS

"The main advantage of the AMD Vitis™ HLS tool, from my perspective, is the design space exploration feature. You can generate different architectures and implementations in a reasonable amount of time by using optimization directives (pipelining, unrolling, etc.). This cannot be done if you code manually with VHDL/Verilog. A nice feature of Vitis HLS is the possibility to do a co-simulation and validation of the HDL-code in order to be sure that the HDL-code is functionally correct." Dr. Frank Kesel - Professor at the University of Pforzheim, Germany Customer Case Study

Documentation

- Based on testing on August 10, 2023, across 1000 Vitis L2/L3 code library designs, with Vitis HLS release 2023.2 vs. Vitis HLS 2023.1. System configuration during testing: Intel Xeon E5-2690 v4 @ 2.6GHz CPU, 256GB RAM, RedHat Enterprise Linux 8.6. Actual performance will vary. System manufacturers may vary configuration, yielding different results. -VGL-04

- The benchmark tests were performed on all 1208 Vitis L1 library C-code designs as of February 12th, 2023. All designs were run using a system with 2P Intel Xeon E5-2690 CPUs with CentOS Linux, SMT enabled, Turbo Boost disabled. Hardware configuration not expected to effect software test results. Results may vary based on software and firmware settings and configurations- VGL-03

Connect with Admissions

Contact J.D. Admissions

Learn more about the law school admissions process and HLS community through our online resources and events this fall. See below to learn how you can connect with HLS, and be sure to register in advance where appropriate.

Want to keep in touch? Fill out the form below to join our mailing list and receive periodic updates from the J.D. Admissions Office.

- Introduce Yourself

J.D. Admissions Events

On-Campus Information Sessions Join us in Cambridge this fall for one of our on-campus information sessions. Members of the J.D. admissions team will facilitate these events, which include an informational presentation, Harvard Law School campus tour, and time for Q&A. All On-Campus Information Sessions will run from 2:00 – 4:00 p.m. ET . Register using the links below.

- Friday, August 30, 2024

- Friday, September 13, 2024

- Friday, September 27, 2024

- Friday, November 1, 2024

- Friday, November 22, 2024

Can’t make it to Cambridge for a visit at one of the times above? Check out our self-guided campus tour and virtual campus tour .

Join one of our virtual J.D. Admissions Q&A Sessions. These events offer the chance to have your questions answered directly by those who read your applications (that’s us!). Members of the J.D. Admissions team will spend 45 minutes answering your pre-submitted questions. Register using the links below.

- Thursday, September 19, 2024 at 3:00 – 3:45 p.m. ET

- Thursday, October 3, 2024 at 8:00 – 8:45 p.m. ET

- Thursday, October 24 at 12:00 – 12:45 p.m. ET

- Thursday, November 14, 2024 at 8:00 – 8:45 p.m. ET

- Thursday, December 12, 2024 at 12:00 – 12:45 p.m. ET

- Thursday, January 9, 2025 at 3:00 – 3:45 p.m. ET

Are you curious to hear from current HLS students who share a background with you? From undergraduate location, school type, to work experience, we’re excited to offer this series of webinars featuring current students from a variety of geographic locations and educational backgrounds. Register using the links below.

General Student Experience Webinars

- Wednesday, September 25, 2024 at 12:30 – 1:15 p.m. ET

- Wednesday, October 16, 2024 at 12:30 – 1:15 p.m. ET

Applying to HLS . . .

from the West

representation from AK, CA, CO, HI, ID, MT, NV, OR, UT, WA, WY

- Monday, October 21, 2024 at 3:45 – 4:30 p.m. ET

from the Southwest

representation from AZ, NM, OK, TX

- Tuesday, October 22, 2024 at 12:30 – 1:15 p.m. ET

from the Midwest

representation from IA, IL, IN, KS, MI, MN, MO, NE, ND, OH, SD, WI

- Wednesday, October 23, 2024 at 12:30 – 1:15 p.m. ET

as International Students

- Thursday, October 24, 2024 at 9:15 – 10:00 a.m. ET

from the Southeast

representation from AL, AR, FL, GA, KY, LA, MS, NC, SC, TN, VA, WV

- Friday, October 25, 2024 at 12:30 – 1:15 p.m. ET

with Military Experience

- Tuesday, October 29, 2024 at 12:30 – 1:15 p.m. ET

from Historically Black Colleges and Universities (HBCUs)

- Wednesday, October 30, 2024 at 12:30 – 1:15 p.m. ET

from Community Colleges

- Thursday, October 31, 2024 at 12:30 – 1:15 p.m. ET

Do you have a question about the application, or a quick admissions inquiry? Drop by and chat live with members of our team during our J.D. Admissions Office Hours.

Stop by at anytime, and stay as long as you like, during these live text-chat sessions. Register using the links below.

Tuesday, October 1, 2024 at 2:00 – 3:00 p.m. ET

Tuesday, November 5, 2024 at 02:00 – 3:00 p.m. ET

Break Into Law Conference (Virtual)

- Saturday, June 22, 2024 at 1:30 – 4:30 p.m. ET

Service2School Vetlink Summit (In-Person)

- Saturday, June 22, 2024 at 2:30 – 3:00 p.m. CT

Boston Law Fair (In-Person)

- Saturday, September 14, 2024 at 10:00 – 1:00 p.m. ET

Atlanta LSAC Law School Forum (In-Person)

- Friday, September 27, 2024 at 12:00 – 6:00 p.m. ET

11th Annual National HBCU Pre-Law Summit & Law Expo 2024 (In-Person)

- Saturday, September 28, 2024 at 5:30 – 7:30 p.m. ET

LSAC Digital Law School Forum (Virtual)

- Wednesday, October 23, 2024 at 5:00 – 8:00 p.m. ET

Boston LSAC Law School Forum (In-Person)

- Saturday, November 2, 2024 at 10:00 – 4:00 p.m. ET

20th Annual National Black Pre-Law Conference and Law Fair (In-Person)

- Saturday, November 16, 2024 at 11:00 – 1:00 p.m. ET

Harvard Graduate Joint Degree Information Session

This event is designed for prospective applicants to learn more about Harvard Business School , Harvard Kennedy School and Harvard Law School . Candidates with an interest in pursuing a joint degree between two of these schools are particularly encouraged to attend. The event will include an admissions panel followed by a fair to learn more about each graduate program. Register below.

- Tuesday, July 16, 2024 at 7:00 – 9:00 p.m. ET (In-Person in Washington, D.C.)

JD/MBA Virtual Information Session

Join us for a virtual information session to learn about the JD/MBA joint degree program. HLS and HBS admissions staff will provide an overview of the program and application process. A panel of students will share their experiences and answer questions.

- Tuesday, August 6, 2024 at 3:00 – 4:00 p.m. ET

The HLS J.D. Admissions team will be visiting college campuses across the United States this fall. See if we will be at your university and register using the link below:

HLS on the Road

Navigating Law School Admissions

After three seasons, we took Navigating Law School Admissions on the road during the fall of 2023. We had so much fun that we are doing it again! We are once again partnering with law firms to host live events in Miami, New York City, and Washington, DC.

We hope you can join us at one of these events. Register below .

Live in Miami

- Wednesday, September 25, 2024 at 5:30 – 6:45 p.m. ET

Live in New York

- Tuesday, October 8, 2024 at 6:00 – 7:30 p.m. ET

Live in Washington D.C.

- Wednesday, October 9, 2024 at 6:00 – 7:15 p.m. ET

JDP and Transfer Admissions Events

Interested in participating in Junior Deferral Program (JDP) or Transfer application information sessions and events? Visit our program pages to learn more.

J.D. Admissions Information Session

Explore hls.

- Admissions Viewbook

- Virtual HLS Campus Tour

- Self-Guided HLS Campus Tour

- Virtual HLS Library Tour

Meet the J.D. Admissions Team

Get to know the J.D. Admissions team.

J.D. Admissions Blog

For insight, stories, and updates from the J.D. Admissions Office at Harvard Law School, visit our blog .

Student Voices: Hands-On Experience Advising Clients

Attending Harvard Law School has provided me with unparalleled opportunities to engage in pro bono work with clients. While continuing my studies, I have been able to expand on my legal education outside of the classroom through Harvard’s many clinics and Student Practice Organizations. HLS’s various organizations ensure there are offerings related to anyone’s interests.

September 25, 2024

2023–2024 by the Numbers

As we fully dive into recruitment season this month, the J.D. Admissions team is reflecting on our previous admissions cycle. We ramped up our recruitment travel last year, visiting almost 90 university and college campuses across the United States and the United Kingdom. We also expanded our virtual outreach, hosting over 50 online events for

September 3, 2024

Connecting with the J.D. Admissions Office in Fall 2024

We are thrilled to welcome the Class of 2027 to campus this week! As we look forward to the rest of the fall, we are already gearing up for recruitment efforts for the Class of 2028. Whether you are interested in learning more about Harvard Law School or seeking guidance on the application process for

August 21, 2024

JDP Reflections: 8 Lessons I Learned Through my Junior Deferral Program Experience

The Harvard Junior Deferral Program (JDP) can take you anywhere you can imagine (sometimes even places you haven’t imagined). JDP provides time before law school to explore other opportunities, the world, and, most importantly, yourself. Reflecting on my two-year deferral time, it is difficult to narrow down all of my experiences from spending time in

August 2, 2024

JDP Reflections: How I Discovered the Junior Deferral Program (JDP)

Why Defer? When I arrived at the University of Virginia in the fall of 2018, I had one thing on my mind: attending law school. However, which school I wanted to attend, what type of lawyer I wanted to be, and, to a certain extent, why I even wanted to be a lawyer were all

July 23, 2024

Modal Gallery

Gallery block modal gallery.

2025 RODEOHOUSTON | MARCH 4 – 23

Countdown to 2025 rodeohouston |, march 4 - 23, 2025.

HOW TO BECOME A

RODEO VOLUNTEER

JOIN MORE THAN 35,000 VOLUNTEERS SERVING ON 110 COMMITTEES.

ECONOMIC IMPACT

quantifying the economic impact and economic activity generated by the 2024 Rodeo.

Educational

Since 1932, more than $600 million has been awarded to texas youth.

OFFICIAL RODEO MERCHANDISE

Acid wash burnout tee, fishing shirt w/ bow-h, youth denim and teal dress, sleeveless polo w/ bow-h, youth howdy ss pearl snap, latest news, record-breaking purse ignites rodeo revolution, rodeo grants texas graduate programs more than $480,000 in assistantship awards, the story behind the rodeo’s proudest hispanic footprint, houston’s birthday, rodeo celebrates texas students with $1.2 million in achievement scholarships, the call to the hall of fame, saddles and sips: the unlikely dance of rodeo and wine, go tejano fashion show, ag mechanics casino night fundraiser, fall committee showcase, archery competition, red, white and boots fundraiser, black heritage fall round up, putting fore paints, 14th annual ranching & wildlife sporting clays classic, black heritage western gala, world’s championship bar-b-que contest, mission statement.

The Houston Livestock Show and Rodeo™ promotes agriculture by hosting an annual, family-friendly experience that educates and entertains the public, supports Texas youth, showcases Western heritage and provides year-round educational support within the community.

AGRICULTURE

Western heritage, entertainment, meet our scholars.

“Receiving the Rodeo Scholarship represents so much more than financial aid; it’s a commitment to my future and belief in my potential. This experience has been nothing short of amazing, and I look forward to the great things this organization will continue to do for future generations to come. Being an HLSR Scholar is an honor that I will forever cherish and be grateful for!”

“ The Houston Livestock Show and Rodeo Scholarship was a transformative blessing that made my college dreams a reality. This opportunity not only allowed me to attend college but also empowered me to set an example for future generations in my family. I am immensely grateful to call myself a Rodeo Scholar. ”

“ This scholarship is so important because it opens opportunities that would otherwise be closed. Aside from the financial benefits, this scholarship honors my hard work and dedication to my schooling and extracurricular activities. ”

“B eing a part of the Houston Stock Show and Rodeo family as a scholar is so important to me because it has given me resources to succeed not only in college but in life! I am so proud to be a part of the family and support a program that gives back to young people and allows them to chase their dreams! ”

RODEOHOUSTON

Rodeohouston® super series.

A 20-day tournament-style competition that crowns an event champion in bareback riding, bull riding, saddle bronc riding, steer wrestling, tie-down roping, team roping, and women’s barrel racing and breakaway roping

Athlete Payout

Total: $2,178,000 Champions: $50,000 + previous round winnings Winnings: Custom-made saddle and belt buckle + an invitation to compete at RODEOHOUSTON the following two years

HERITAGE PARTNERS

课时3:Vitis HLS设计流程(实例演示)——Vitis HLS教程

课时3:Vitis HLS设计流程(实例演示)

2. vitis hls设计注意事项, 3. vitis hls设计示例, 3.1 vitis hls工程建立, 3.3 创建另一个solution.

算法或软件的设计和仿真都基于C/C++,通过HLS平台导出打包好的IP RTL代码,最后将该打包的IP加入到主工程使用。

本课时,我们通过一个具体的实例,演示HLS设计流程。

在Vitis HLS中,只有一个函数可以设为顶层综合函数,但不能是main()函数。

有些代码和结构是不可被Vitis HLS综合的,包括动态分配存储空间、与操作系统相关操作等。

- 在写C代码的时候,对于每个for循环,最好都创建一个标签(如该例程中的“myloop”标签)。这样有利于后期对每个循环添加不同的directives;

- main()函数的返回值,在没有错误的时候,返回值设为0,有错误的时候,返回值设为1,这样有利于判断仿真是否出错;

参考文献: [1]《Vitis High-Level Synthesis User Guide》. UG1399. Xilinx [2] “跟Xilinx SAE学HLS系列视频讲座-高亚军 ”https://www.bilibili.com/video/av41246874

如果大家对我们的文章感兴趣,可以关注我们的公众号:“FpgaHome”,实时关注我们的更新动态。 该工程对应的源码可以通过关注该微信公众号,在公众号输入“HLS_DEMO”来获取工程的下载链接,工程采用的是Vitis HLS 2021.1版本。

请填写红包祝福语或标题

1.余额是钱包充值的虚拟货币,按照1:1的比例进行支付金额的抵扣。 2.余额无法直接购买下载,可以购买VIP、付费专栏及课程。

Modal Gallery

Vitis HLS - 2024.1 English

Vitis tutorials: getting started (xd098).

Version: Vitis 2024.1

Introduction

Vitis High-Level Synthesis (HLS) lets you compile C/C++ code into RTL code for implementation in the programmable logic (PL) region of AMD devices. It is the tool that performs high-level synthesis of the C/C++ code and exports it as either a Vivado IP (.zip) for use in the Vivado Design Suite and the Embedded Software development flow, or as a Vitis kernel (.xo) for use in the Vitis acceleration flow and heterogeneous system designs. Although the Vitis kernel and Vivadp IP flows are similar, there are some fundamental differences as explained in Introduction to Vitis HLS Components . This tutorial demonstrates the Vitis unified IDE flow for the bottom-up development of HLS designs.

Before You Begin

The labs in this tutorial use:

BASH Linux shell commands.

2024.1 Vitis core development kit release.

IMPORTANT: Before running any of the examples, make sure you have installed the Vitis core development kit as described in Installation in the Application Acceleration Development flow of the Vitis Unified Software Platform Documentation (UG1416). If you run applications on the AMD Alveo™ Data Center accelerator cards, ensure the card and software drivers have been correctly installed by following the instructions To complete installation, follow the instructions on the Alveo Product Documentation tab .

Setup the environment to run Vitis

To configure the environment to run Vitis, run the following scripts which set up the environment to run in a specific command shell.

NOTE: .csh scripts are also provided but this tutorial assumes a bash shell is used.

To specify the location of any Data-Center or Embedded platforms you have installed, set the following environment variable:

NOTE: On some Ubuntu distributions, you must also export LIBRARY_PATH to properly set up Vitis.

For more information see AMD AR 73698 .

Accessing the Tutorial Reference Files

To access the reference files, type the following into a terminal: git clone https://github.com/Xilinx/Vitis-Tutorials .

Navigate to the Getting_Started/Vitis_HLS directory, and then access the reference-files directory.

This tutorials presents Using the Vitis unified IDE for creating an HLS component:

line 20 .../span> for creating an HLS component:

Return to Main Page — Return to Main Page — line 20 ...e target is not in the archive or the link malformed ?'>Return to Main Page — Return to Getting Started Pathway

Return to Getting Started Pathway

Copyright © 2020–2023 Advanced Micro Devices, Inc

Terms and Conditions

Navigation Menu

Search code, repositories, users, issues, pull requests..., provide feedback.

We read every piece of feedback, and take your input very seriously.

Saved searches

Use saved searches to filter your results more quickly.

To see all available qualifiers, see our documentation .

- Notifications You must be signed in to change notification settings

Xilinx/Vitis-HLS-Introductory-Examples

Folders and files, repository files navigation.

Introductory examples for Vitis HLS

Copyright 1986-2022 Xilinx, Inc. All Rights Reserved. Copyright 2022-2024 Advanced Micro Devices, Inc. All Rights Reserved.

Licensed under the Apache License, Version 2.0 (the "License"); you may not use this file except in compliance with the License. You may obtain a copy of the License at

Unless required by applicable law or agreed to in writing, software distributed under the License is distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License for the specific language governing permissions and limitations under the License.

C/C++ synthesizable examples

Each example comes with C/C++ source code, a README, and script or config file. The examples are organized in categories denoted by the directory names:

- Appnotes: A DSP design, a legacy digital up converter appnote.

- Array: Show how to partition memory arrays.

- Interface: Common examples for interface protocols.

- Misc.: Other examples such as the RTL blackbox flow and the LogiCore FFT from Vivado.

- Modelling: The essentials for loops, arbitrary precision types and vectors.

- Pipelining: Illustrating one of the most fundamental concept of HLS.

- Task_Level_Parallelism: Dataflow and free running streams with hls::task.

- Vitis: Kernel examples for the software acceleration flow.

Running the examples at the command line

- vitis-run --mode hls --tcl run_hls.tcl

- vitis_hls -f run_hls.tcl

Note that by default only C simulation and C synthesis will run. Change the value of hls_exec in the Tcl script to run co-simulation and Vivado implementation.

Contributors 9

- Python 2.3%

- Makefile 0.7%

- Verilog 0.3%

COMMENTS

Located in the heart of Cambridge, Harvard Law School is in close proximity to a variety of accommodations, historical sites, restaurants and attractions. Learn more about the daily structure of our programs and about the Boston and Cambridge areas.

The AMD Vitis™ HLS tool allows users to easily create complex FPGA algorithms by synthesizing a C/C++ function into RTL. The Vitis HLS tool is tightly integrated with both the Vivado™ Design Suite for synthesis and place & route and the Vitis™ unified software platform for heterogenous system designs and applications.

Listen as experts at Harvard Law School discuss, debate, and explain key trends and milestones in United States and international law and legal education. From landmark Supreme Court decisions to federal and state laws to trends in American society, get the latest legal scholarship on many of the most vital issues of the day by tuning into ...

Learn more about the law school admissions process and HLS community through our online resources and events this fall. See below to learn how you can connect with HLS, and be sure to register in advance where appropriate.

Immerse yourself in the heart of Texas tradition at the Houston Livestock Show and Rodeo. Explore exhilarating rodeo events, world-class entertainment, and educational exhibits.

那么用户以后如果想要在 Vitis HLS 里综合出更好的电路,可以自己定制或者从网上下载别人设计好的 LLVM pass 插件在 LLVM IR 的层面进行进一步自动优化。 几周前我收到了来自 Xilinx 团队的 Vitis HLS 2020.1 beta 版本。

课时2我们介绍了Vitis HLS的设计流程,如下图所示: 算法或软件的设计和仿真都基于C/C++,通过HLS平台导出打包好的IP RTL代码,最后将该打包的IP加入到主工程使用。 本课时,我们通过一个具体的实例,演示HLS设计流程。 2. Vitis HLS设计注意事项. 在Vitis HLS中,只有一个函数可以设为顶层综合函数,但不能是main ()函数。 任何在顶层函数下的子函数都会被综合,并且综合后得到代码的函数层级结构可以保留。 有些代码和结构是不可被Vitis HLS综合的,包括动态分配存储空间、与操作系统相关操作等。 3. Vitis HLS设计示例. 3.1 Vitis HLS工程建立. (1)新建Vitis HLS工程,如下图所示,工程名为“HLS_StartDemo”;

This page includes all upcoming in-person events hosted by the HLS J.D. Admissions Office, including information sessions, campus visits, and more. The calendar is updated as additional events are scheduled. To view our virtual events, please visit our Connect with Admissions webpage.

Loading application... | Technical Information Portal

Modelling: The essentials for loops, arbitrary precision types and vectors. Pipelining: Illustrating one of the most fundamental concept of HLS. Task_Level_Parallelism: Dataflow and free running streams with hls::task. Vitis: Kernel examples for the software acceleration flow.